### VO 050041:

# Technische Grundlagen der Informatik

Begleitende Folien zur Vorlesung

Wintersemester 2016/17

Vortragende: Peter Reichl, Andreas Janecek

Zuletzt aktualisiert: 30. November 2016

# Teil 5: Rechnerarchitekturen

# Outline: Teil 5

- 1 Einführung und Formale Aspekte Klassifikation Design und Performance Quantitative Methoden

- 2 Standard-Rechnerarchitektur Abstraktionsebenen Prozessor

- Speicherverwaltung Virtueller Speicher und Paging Caching

- 4 Externer Speicher Festplatten Disk Scheduling SSD

- Skalare und superskalare/parallele Architekturen CISC und RISC Pipelining Superskalare Architekturen

### Literatur

- Mikroprozessortechnik (Wüst): Kapitel 6, 7, 10, 11, 13

- Computer Architecture (Hennessy, Patterson): Kapitel 1, 2, Appendix A, B, C

# Überblick

- Einführung und Formale Aspekte

Klassifikation

Design und Performance

Quantitative Methoden

- 2 Standard-Rechnerarchitektur Abstraktionsebenen

- Speicherverwaltung Virtueller Speicher und Paging Caching

- 4 Externer Speicher Festplatten Disk Scheduling

- Skalare und superskalare/parallele Architekturen CISC und RISC Pipelining Superskalare Architekturen

Klassifikation

### Aufbau von Rechnern

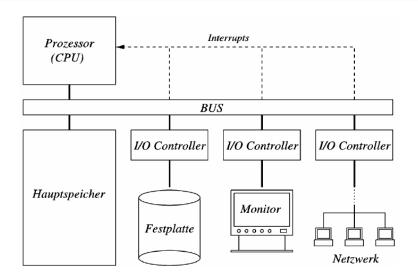

### Grundlegende Komponenten eines Computers

- (Mikro-)Prozessor (CPU): verarbeitet Daten

- Speicher: Arbeitsspeicher, Massenspeicher

- Ein-/Ausgabegeräte: Tastatur, Display, Drucker, ...

- Busse: Interne Kommunikationsleitungen

└ Klassifikation

### Aufbau von Rechnern

- Klassifikation

### Klassifikationskriterien

#### Rechner lassen sich nach mehreren Kriterien klassifizieren:

- Preis/Leistungsfähigkeit

- Laptop: mobile und/oder nomadische Nutzung durch einen Anwender, Netzanbindung über WLAN

- Personal Computer (PC): typischerweise ein Anwender, netzwerkfähig (d.h. Ressourcen können von anderen Benutzern mitverwendet werden)

- Workstation (Arbeitsplatzrechner): in der Regel mit Mehrbenutzer-Betriebssystem und Netz ausgestattet

- Mainframe (Grossrechner): Hochgeschwindigkeitsrechner, von vielen Anwendern gleichzeitig benutzt

- Grenzen zwischen diesen Kategorien sind fliessend!

- Maschinenbefehlssatz (CISC vs RISC) → später!!

- Anzahl der Daten- und Befehlsströme → Flynn

# Rechner-Klassifikation nach Flynn

### Anzahl der vorhandenen Datenströme

- SD: Single Data Stream

- MD: Multiple Data Streams

#### Anzahl der vorhandenen Befehlsströme

- SI: Single Instruction Stream

- MI: Multiple Instruction Streams

- SISD

- SIMD

- MISD

- MIMD

-Klassifikation

### SISD

#### SISD - Single Instruction, Single Data

- Sequenzielle Programmausführung (ein Prozessor)

- Princeton-Architektur ("von Neumann-Rechner")

- Gemeinsamer Speicher für Instruktionen und Daten

- Streng sequentieller (deterministischer) Programmablauf garantiert

- Bei wechselndem Daten-/Programmspeicher-Bedarf gute Auslastung: "Von Neumann Bottleneck"

- Harvard-Architektur:

- Getrennter Speicher für Instruktionen und Daten

- Zwei unabhängige (unterschiedlich breite) Busse

- Daten und Befehle können gleichzeitig geladen werden

- Aber: Race conditions, nicht-deterministischer Programmablauf

- Klassifikation

## **SIMD**

### SIMD - Single Instruction, Multiple Data

Instruktion gleichzeitig auf mehrere Datensätze ausführen

$$\bullet \begin{pmatrix} 3 \\ -2 \\ 0 \\ 7 \end{pmatrix} \cdot 9 = \begin{pmatrix} 27 \\ -18 \\ 0 \\ 63 \end{pmatrix}$$

- Vektorrechner: 1 Operation; SISD: 4 Operationen

- Mathematische, physikalische Berechnungen, auch Grafik

- General Purpose Graphics Processing Unit (GPGPU)

- Auch viele moderne Mikroprozessoren besitzen inzwischen SIMD-Erweiterungen

Einführung und Formale Aspekte

-Klassifikation

### **MIMD**

#### MIMD - Multiple Instruction, Multiple Data

- Mehrere Prozessoren, mit Leitwerk und Rechenwerk

- Jeder arbeitet eigenständig

- MIMD Computer kann mehrere unabhängige Programme gleichzeitig ausführen

Einführung und Formale Aspekte

Design und Performance

# Computerdesign

- Wir wollen einen neuen, optimalen Computer kaufen/bauen

- Oder wir wollen verschiedene existierende vergleichen

Design und Performance

# Computerdesign

- Wir wollen einen neuen, optimalen Computer kaufen/bauen

- Oder wir wollen verschiedene existierende vergleichen

- Was aber ist eigentlich optimal?

# Computerdesign

- Wir wollen einen neuen, optimalen Computer kaufen/bauen

- Oder wir wollen verschiedene existierende vergleichen

- Was aber ist eigentlich optimal?

- · Welche Tasks?

# Computerdesign

- Wir wollen einen neuen, optimalen Computer kaufen/bauen

- Oder wir wollen verschiedene existierende vergleichen

- Was aber ist eigentlich optimal?

- · Welche Tasks?

- Welche Programme?

# Computerdesign

- Wir wollen einen neuen, optimalen Computer kaufen/bauen

- Oder wir wollen verschiedene existierende vergleichen

- Was aber ist eigentlich optimal?

- · Welche Tasks?

- Welche Programme?

- Welcher Benutzer?

# Computerdesign

- Wir wollen einen neuen, optimalen Computer kaufen/bauen

- Oder wir wollen verschiedene existierende vergleichen

- Was aber ist eigentlich optimal?

- · Welche Tasks?

- Welche Programme?

- Welcher Benutzer?

- · Schnelligkeit?

Design und Performance

# Computerdesign

- Wir wollen einen neuen, optimalen Computer kaufen/bauen

- Oder wir wollen verschiedene existierende vergleichen

- Was aber ist eigentlich optimal?

- · Welche Tasks?

- Welche Programme?

- Welcher Benutzer?

- · Schnelligkeit?

- Zuverlässigkeit?

- Einführung und Formale Aspekte

Design und Performance

# Computerdesign

- Wir wollen einen neuen, optimalen Computer kaufen/bauen

- Oder wir wollen verschiedene existierende vergleichen

- Was aber ist eigentlich optimal?

- · Welche Tasks?

- Welche Programme?

- Welcher Benutzer?

- · Schnelligkeit?

- Zuverlässigkeit?

- Physische Robustheit?

- ..

- Einführung und Formale Aspekte

Design und Performance

# Computerdesign

- Wir wollen einen neuen, optimalen Computer kaufen/bauen

- Oder wir wollen verschiedene existierende vergleichen

- Was aber ist eigentlich optimal?

- Welche Tasks?

- Welche Programme?

- Welcher Benutzer?

- · Schnelligkeit?

- Zuverlässigkeit?

- Physische Robustheit?

- ..

- Wir brauchen eine Metrik, um Vergleichbarkeit herzustellen

- Einführung und Formale Aspekte

Design und Performance

# Beispiele

#### **Desktops**

- Optimum an Preis und Performance (Preis/Leistung)

- Oft: Preis für Mindestanforderungen (z.B. Office)

Einführung und Formale Aspekte

Design und Performance

# Beispiele

### Desktops

- Optimum an Preis und Performance (Preis/Leistung)

- Oft: Preis für Mindestanforderungen (z.B. Office)

#### Server

- Verfügbarkeit und Zuverlässigkeit

- Skalierbarkeit: Rechenleistung, Speicher, I/O, ...

- Durchsatz: Transaktionen pro Zeiteinheit

VO 050041: Technische Grundlagen der Informatik

Einführung und Formale Aspekte

Design und Performance

# Beispiele

#### Desktops

- Optimum an Preis und Performance (Preis/Leistung)

- Oft: Preis f

ür Mindestanforderungen (z.B. Office)

#### Server

- Verfügbarkeit und Zuverlässigkeit

- Skalierbarkeit: Rechenleistung, Speicher, I/O, ...

- Durchsatz: Transaktionen pro Zeiteinheit

### Dynamische Entwicklung

- Stromverbrauch pro Durchsatz

- **.** . . .

Design und Performance

### Performance

### Wichtige Kriterien

- "Computer A ist schneller als Computer B" muss quantifizierbar sein

- Durchsatz (Throughput, X [Aufträge/s]): Mittlere Anzahl von erledigten Aufträgen pro Zeiteinheit. Je größer, desto besser.

- Ausführungszeit (Execution Time, ET, [s]): Zeit zwischen Beginn und Ende eines Auftrags. Je kleiner, desto besser.

Einführung und Formale Aspekte

Design und Performance

### Execution time und Performance

### Rechner X ist n-mal so schnell wie Rechner Y

$$\frac{ET_Y}{ET_X} = r$$

### **Execution time und Performance**

### Rechner X ist n-mal so schnell wie Rechner Y

$$\frac{ET_Y}{ET_X} = n$$

#### ET ist reziprok zu Performance

$$n = \frac{ET_Y}{ET_X} = \frac{Performance_X}{Performance_Y}$$

### **Execution time und Performance**

#### Rechner X ist n-mal so schnell wie Rechner Y

$$\frac{ET_Y}{ET_X} = n$$

#### ET ist reziprok zu Performance

$$n = \frac{ET_Y}{ET_X} = \frac{Performance_X}{Performance_Y}$$

### Beispiel

Durchsatz von X ist 1.3 mal so hoch wie von Y  $\Rightarrow$  auf Rechner X können 1.3 mal so viele Tasks pro Zeiteinheit erledigt werden wie auf Rechner Y.

# Zeit-Begriffe

#### **Execution Time**

- Verschiedene Definitionen möglich

- Response time (wall clock time): Gesamte Zeit vom Absenden der Anfrage bis zum Eintreffen der Antwort.

- CPU time: Nur Zeit, in der CPU aktiv ist (z.B. keine Wartezeiten)

- User CPU time: Nur Zeit, die CPU für das Programm aufwendet (user mode)

- System CPU time: Nur Zeit, die CPU für Betriebssystemaufgaben (für Programm) aufwendet (kernel mode)

- Linux/UNIX: time Kommando, z.B.: time firefox

Design und Performance

# Leistungsvergleich

• Welcher der Computer hat die höchste Performance?

|            | Computer A | Computer B | Computer C |

|------------|------------|------------|------------|

| Programm 1 | 1s         | 10s        | 60s        |

| Programm 2 | 199s       | 100s       | 60s        |

| Programm 3 | 50s        | 140s       | 130s       |

|            |            |            |            |

Design und Performance

# Leistungsvergleich

• Welcher der Computer hat die höchste Performance?

|            | Computer A | Computer B | Computer C |

|------------|------------|------------|------------|

| Programm 1 | 1s         | 10s        | 60s        |

| Programm 2 | 199s       | 100s       | 60s        |

| Programm 3 | 50s        | 140s       | 130s       |

| Total ET   | 250s       | 250s       | 250s       |

Gesamt-Ausführungszeit vereinfacht Interpretation

Lesign und Performance

# Leistungsvergleich - Möglichkeiten

#### **Arithmetisches Mittel**

$$\overline{ET} = \frac{1}{n} \cdot \sum_{i=1}^{n} ET_{i} [s]$$

# Leistungsvergleich - Möglichkeiten

#### **Arithmetisches Mittel**

$$\overline{ET} = \frac{1}{n} \cdot \sum_{i=1}^{n} ET_{i} [s]$$

### Gewichtete Ausführungszeit (weighted ET)

- Für ungleich verteilte Workloads

- Z.B. 20% der Tasks betreffen P1, 80% P2, dann sind Gewichte  $g_1 = 0.2$  bzw.  $g_2 = 0.8$

$$WET = \sum_{i=1}^{n} g_i \cdot ET_i \ [s]$$

Einführung und Formale Aspekte

Design und Performance

# Designprinzipien

### Designprinzipien

- "Make the common case fast"

- Häufig auftretende Ereignisse schnell abarbeiten

- Seltene Ereignisse nicht übermäßig beachten

- Welche Gesamt-Verbesserung können wir erwarten?

Quantitative Methoden

## Gesetz von Amdahl

# Definiert den <u>Gesamt</u>-Speedup S, der mit einer <u>Teil</u>-Verbesserung erzielt werden kann!

$$S = \frac{ET_{alt}}{ET_{neu}}$$

$$ET_{neu} < ET_{alt}$$

Quantitative Methoden

## Gesetz von Amdahl

#### Fraction Enhanced F<sub>F</sub>

- Anteil der Gesamt-ET, der verbessert (beschleunigt) ist

- Bsp: Von einer Gesamt-ET von 60s wurden 20s verbessert  $\Rightarrow F_E = \frac{20}{60} = \frac{1}{3}$

- Es gilt: F<sub>F</sub> ≤ 1

### Gesetz von Amdahl

#### Fraction Enhanced $F_F$

- Anteil der Gesamt-ET, der verbessert (beschleunigt) ist

- Bsp: Von einer Gesamt-ET von 60s wurden 20s verbessert  $\Rightarrow F_E = \frac{20}{60} = \frac{1}{3}$

- Es gilt: F<sub>E</sub> ≤ 1

### Speedup Enhanced SE

- Faktor, um den der erwähnte Anteil der Gesamt-ET (F<sub>E</sub>) verbessert (beschleunigt) ist

- Bsp: Für das gleiche Teil-Problem statt 5s nur noch 2s benötigt: ⇒ S<sub>E</sub> = <sup>5</sup>/<sub>2</sub>

- Es gilt: *S<sub>E</sub>* > 1

Quantitative Methoden

### Gesetz von Amdahl

### Herleitung

$$S = \frac{ET_{alt}}{ET_{neu}} = \frac{ET_{alt}}{ET_{alt} \cdot \left(\underbrace{(1 - F_E)}_{unverbessert} + \underbrace{\frac{F_E}{S_E}}_{verbessert}\right)} \Rightarrow$$

Quantitative Methoden

### Gesetz von Amdahl

### Herleitung

$$S = \frac{ET_{alt}}{ET_{neu}} = \frac{ET_{alt}}{ET_{alt} \cdot \left(\underbrace{(1 - F_E)}_{unverbessert} + \underbrace{\frac{F_E}{S_E}}_{verbessert}\right)} \Rightarrow$$

#### Amdahl's Law

$$\Rightarrow S = \frac{1}{(1 - F_E) + \frac{F_E}{S_F}}$$

-Quantitative Methoden

### Gesetz von Amdahl

#### Anwendung

- Gibt Hinweise, inwieweit eine Verbesserung überhaupt die Gesamt-Performance steigert (steigern kann)

- Gibt eine Grenze des Speedups an, der vor allem von der  $F_E$  abhängt  $(\lim_{S_E \to \infty} S = \frac{1}{1 F_E})$

- Hilft auch bei der Beurteilung, welche von zwei Verbesserungsvarianten besser ist!

-Quantitative Methoden

## Amdahl: Beispiel

### Beispiel fernab der IT (?)

Wir arbeiten alleine an einem Projekt

-Quantitative Methoden

## Amdahl: Beispiel

- Wir arbeiten alleine an einem Projekt

- 40% der Zeit für geht für Meetings, Koordination, etc. drauf

-Quantitative Methoden

## Amdahl: Beispiel

- Wir arbeiten alleine an einem Projekt

- 40% der Zeit f

ür geht f

ür Meetings, Koordination, etc. drauf

- 60% der Zeit kann produktiv gearbeitet werden

-Quantitative Methoden

## Amdahl: Beispiel

- Wir arbeiten alleine an einem Projekt

- 40% der Zeit f

ür geht f

ür Meetings, Koordination, etc. drauf

- 60% der Zeit kann produktiv gearbeitet werden

- Projekt verzögert sich, 5 neue Mitarbeiter eingestellt

- Quantitative Methoden

## Amdahl: Beispiel

- Wir arbeiten alleine an einem Projekt

- 40% der Zeit f

ür geht f

ür Meetings, Koordination, etc. drauf

- 60% der Zeit kann produktiv gearbeitet werden

- Projekt verzögert sich, 5 neue Mitarbeiter eingestellt

- Einfache Annahme: 40:60-Verhältnis gilt weiterhin

-Quantitative Methoden

## Amdahl: Beispiel

- Wir arbeiten alleine an einem Projekt

- 40% der Zeit f

ür geht f

ür Meetings, Koordination, etc. drauf

- 60% der Zeit kann produktiv gearbeitet werden

- Projekt verzögert sich, 5 neue Mitarbeiter eingestellt

- Einfache Annahme: 40:60-Verhältnis gilt weiterhin

- Mit welchem Speedup ist maximal zu rechnen?

- Warum wird dieser praktisch wahrscheinlich nicht halten?

Quantitative Methoden

$$S = \frac{1}{(1 - F_E) + \frac{F_E}{S_E}} =$$

Quantitative Methoden

$$S = \frac{1}{(1 - F_E) + \frac{F_E}{S_E}} = \frac{1}{(1 - 0.6) + \frac{0.6}{6}}$$

Quantitative Methoden

$$S = \frac{1}{(1 - F_E) + \frac{F_E}{S_E}} = \frac{1}{(1 - 0.6) + \frac{0.6}{6}}$$

$$= \frac{1}{0.4 + 0.1} =$$

Quantitative Methoden

$$S = \frac{1}{(1 - F_E) + \frac{F_E}{S_E}} = \frac{1}{(1 - 0.6) + \frac{0.6}{6}}$$

$$= \frac{1}{0.4 + 0.1} = \frac{1}{0.5} = \mathbf{2}$$

Quantitative Methoden

## Amdahl: Beispiel

$$S = \frac{1}{(1 - F_E) + \frac{F_E}{S_E}} = \frac{1}{(1 - 0.6) + \frac{0.6}{6}}$$

$$= \frac{1}{0.4 + 0.1} = \frac{1}{0.5} = \mathbf{2}$$

Mitarbeiterzahl versechsfacht (1 ⇒ 6), aber nur Speedup von 2! -Quantitative Methoden

$$S = \frac{1}{(1 - F_E) + \frac{F_E}{S_E}} = \frac{1}{(1 - 0.6) + \frac{0.6}{6}}$$

$$= \frac{1}{0.4 + 0.1} = \frac{1}{0.5} = \mathbf{2}$$

- Mitarbeiterzahl versechsfacht  $(1 \Rightarrow 6)$ , aber nur Speedup von 2!

- Absurdes Experiment: Mitarbeiterzahl unendlich groß machen:  $S = \frac{1}{1 F_r + 0} = 2.5$

-Quantitative Methoden

## Amdahl: Beispiel 2

#### Beispiel aus der IT

Gesamt-ET eines Programm: 30% CPU-Berechnungen, 70% Warten auf Daten aus Arbeitsspeicher

-Quantitative Methoden

## Amdahl: Beispiel 2

#### Beispiel aus der IT

- Gesamt-ET eines Programm: 30% CPU-Berechnungen, 70% Warten auf Daten aus Arbeitsspeicher

- Zwei alternative Varianten der Verbesserung:

- 1 Neue CPU kaufen, die 1.5 mal so schnell rechnen kann

-Quantitative Methoden

## Amdahl: Beispiel 2

#### Beispiel aus der IT

- Gesamt-ET eines Programm: 30% CPU-Berechnungen, 70% Warten auf Daten aus Arbeitsspeicher

- Zwei alternative Varianten der Verbesserung:

- 1 Neue CPU kaufen, die 1.5 mal so schnell rechnen kann

- Neues Mainboard/Speicher kaufen, Transfer zwischen Speicher/CPU 1.4 mal so schnell

-Quantitative Methoden

## Amdahl: Beispiel 2

#### Beispiel aus der IT

- Gesamt-ET eines Programm: 30% CPU-Berechnungen, 70% Warten auf Daten aus Arbeitsspeicher

- Zwei alternative Varianten der Verbesserung:

- 1 Neue CPU kaufen, die 1.5 mal so schnell rechnen kann

- 2 Neues Mainboard/Speicher kaufen, Transfer zwischen Speicher/CPU 1.4 mal so schnell

- Zeigen Sie, welcher Ansatz besser ist, indem Sie den jeweiligen Speedup berechnen und dann vergleichen!

Quantitative Methoden

## Amdahl: Beispiel 2 Lösung

### Variante 1, CPU-Verbesserung

$$S = \frac{1}{(1 - 0.3) + \frac{0.3}{1.5}} = 1.11...$$

-Quantitative Methoden

# Amdahl: Beispiel 2 Lösung

#### Variante 1, CPU-Verbesserung

$$S = \frac{1}{(1-0.3) + \frac{0.3}{1.5}} = 1.11...$$

### Variante 2, Speicherverbesserung

$$S = \frac{1}{(1-0.7) + \frac{0.7}{1.4}} = 1.25...$$

—Quantitative Methoden

## Amdahl: Beispiel 2 Lösung

### Variante 1, CPU-Verbesserung

$$S = \frac{1}{(1 - 0.3) + \frac{0.3}{1.5}} = 1.11...$$

#### Variante 2, Speicherverbesserung

$$S = \frac{1}{(1-0.7) + \frac{0.7}{1.4}} = 1.25...$$

### Lösung

#### Variante 2 ist besser!

(solange man Anschaffungskosten nicht miteinbezieht...)

- Quantitative Methoden

### **CPU-Performance**

- Alle Einheiten und Operationen in einer CPU müssen zeitlich synchronisiert werden

- Taktgeber mit konstanter Frequenz erzeugt diskrete Zeitschritte

- Begriffe: ticks, cycles, clock cycles, ...

-Quantitative Methoden

### **CPU-Performance**

- Alle Einheiten und Operationen in einer CPU müssen zeitlich synchronisiert werden

- Taktgeber mit konstanter Frequenz erzeugt diskrete Zeitschritte

- Begriffe: ticks, cycles, clock cycles, ...

- Zeitdauer eines Takts t<sub>cc</sub>, [s]

### **CPU-Performance**

- Alle Einheiten und Operationen in einer CPU müssen zeitlich synchronisiert werden

- Taktgeber mit konstanter Frequenz erzeugt diskrete Zeitschritte

- Begriffe: ticks, cycles, clock cycles, ...

- Zeitdauer eines Takts t<sub>cc</sub>, [s]

- Taktfrequenz (Taktrate) f, [Hz] = Anzahl an Cycles pro Sekunde (entscheidend für die in einer Sekunde ausführbaren Instruktionen/Operationen)

-Quantitative Methoden

### **CPU-Performance**

- Alle Einheiten und Operationen in einer CPU müssen zeitlich synchronisiert werden

- Taktgeber mit konstanter Frequenz erzeugt diskrete Zeitschritte

- Begriffe: ticks, cycles, clock cycles, ...

- Zeitdauer eines Takts t<sub>cc</sub>, [s]

- Taktfrequenz (Taktrate) f, [Hz] = Anzahl an Cycles pro Sekunde (entscheidend für die in einer Sekunde ausführbaren Instruktionen/Operationen)

- Jede Instruktion benötigt eine gewisse Anzahl an Cycles

-Quantitative Methoden

### **CPU-Performance**

- Alle Einheiten und Operationen in einer CPU müssen zeitlich synchronisiert werden

- Taktgeber mit konstanter Frequenz erzeugt diskrete Zeitschritte

- Begriffe: ticks, cycles, clock cycles, ...

- Zeitdauer eines Takts t<sub>cc</sub>, [s]

- Taktfrequenz (Taktrate) f, [Hz] = Anzahl an Cycles pro Sekunde (entscheidend für die in einer Sekunde ausführbaren Instruktionen/Operationen)

- Jede Instruktion benötigt eine gewisse Anzahl an Cycles

- Ein Programm ist eine Abfolge von Instruktionen

VO 050041: Technische Grundlagen der Informatik

Einführung und Formale Aspekte

Quantitative Methoden

### **CPU-Zeit**

### CPU-Zeit t<sub>CPU</sub>

- $t_{CPU} = (CPU \ clock \ cycles \ fuer \ ein \ Programm) \cdot t_{cc}$

- $t_{CPU} = \frac{(CPU \ clock \ cycles \ fuer \ ein \ Programm)}{f}$

- tcc... Zeitdauer eines Takts [s]

Quantitative Methoden

### **CPU-Zeit**

### CPU-Zeit t<sub>CPU</sub>

- $t_{CPU} = (CPU \ clock \ cycles \ fuer \ ein \ Programm) \cdot t_{cc}$

- $t_{CPU} = \frac{(CPU \ clock \ cycles \ fuer \ ein \ Programm)}{f}$

- t<sub>cc</sub>... Zeitdauer eines Takts [s]

### Clock Cycles Per Instruction (CPI)

- Programm = Anzahl von Instruktionen ⇒ Instruction Count (IC)

- Mittlere Anzahl an Zyklen pro Instruktion oft wichtig

- Auch invers (Instructions per Cycle, IPC) verwendet

$$\mathit{CPI} = \frac{(\mathit{CPU clock cycles pro Programm})}{\mathit{IC}}$$

Quantitative Methoden

## **CPU-Zeit per CPI**

### **CPU-Zeit**

- $t_{CPU} = IC \cdot t_{cc} \cdot CPI$   $t_{CPU} = \frac{IC \cdot CPI}{f}$

Quantitative Methoden

## **CPU-Zeit per CPI**

#### **CPU-Zeit**

- $t_{CPU} = IC \cdot t_{cc} \cdot CPI$   $t_{CPU} = \frac{IC \cdot CPI}{f}$

### Überprüfung

$$\frac{\textit{Instruktionen}}{\textit{Programm}} \cdot \frac{\textit{ClockCycles}}{\textit{Instruktion}} \cdot \frac{\textit{Sekunden}}{\textit{ClockCycle}} = \frac{\textit{Sekunden}}{\textit{Programm}} = \textit{ET}_{\textit{cpu}}$$

—Quantitative Methoden

## CPU-Zeit per CPI

#### **CPU-Zeit**

- $t_{CPU} = IC \cdot t_{cc} \cdot CPI$

- $t_{CPU} = \frac{IC \cdot CPI}{f}$

### Überprüfung

$$\frac{\textit{Instruktionen}}{\textit{Programm}} \cdot \frac{\textit{ClockCycles}}{\textit{Instruktion}} \cdot \frac{\textit{Sekunden}}{\textit{ClockCycle}} = \frac{\textit{Sekunden}}{\textit{Programm}} = \textit{ET}_{\textit{cpu}}$$

### Wichtige Kriterien für CPU-Performance

- · Clock cycle time bzw. invers: Taktrate

- · Cycles per Instruction bzw. invers: Instructions per Cycle

- Instruction count, also "Größe" des Programms

Quantitative Methoden

### CPU-Zeit bei verschiedenen Instruktionen

#### CPU-Zeit bei verschiedenen Instruktionen

- Programme bestehen fast immer aus mehreren, verschiedenen Arten von Instruktionen

- Verschiedene Instruktionen benötigen oft unterschiedliche Mengen an Zyklen

- IC<sub>i</sub>: Anzahl der Instruktionen vom Typ i in einem Programm

- CPI<sub>i</sub>: Mittlere Anzahl der Zyklen/Instruktion vom Typ i

-Quantitative Methoden

### CPU-Zeit bei verschiedenen Instruktionen

#### CPU-Zeit bei verschiedenen Instruktionen

- Programme bestehen fast immer aus mehreren, verschiedenen Arten von Instruktionen

- Verschiedene Instruktionen benötigen oft unterschiedliche Mengen an Zyklen

- IC<sub>i</sub>: Anzahl der Instruktionen vom Typ i in einem Programm

- CPI<sub>i</sub>: Mittlere Anzahl der Zyklen/Instruktion vom Typ i

#### **CPU-Zeit**

$$\textbf{CpuZeit} = \left(\sum_{i=1}^{n} \textbf{IC}_{i} \cdot \textbf{CPI}_{i}\right) \cdot \textbf{t}_{\textbf{cc}}$$

### Überblick

- 1 Einführung und Formale Aspekte Klassifikation Design und Performance Quantitative Methoden

- 2 Standard-Rechnerarchitektur Abstraktionsebenen Prozessor

- Speicherverwaltung Virtueller Speicher und Paging Caching

- 4 Externer Speicher Festplatten Disk Scheduling

- Skalare und superskalare/parallele Architekturen CISC und RISC Pipelining Superskalare Architekturen

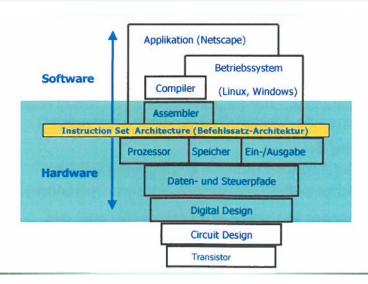

Abstraktionsebenen

#### Abstraktionsebenen

Was ist überhaupt ein Rechner?

- Abstraktionsebenen

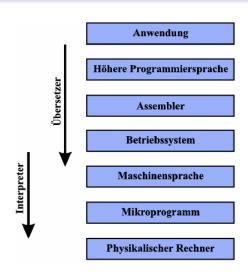

## Abstraktionsebenen

#### Was ist überhaupt ein Rechner?

Antwort hängt stark von der Sichtweise ab:

- Anwendungs-Ebene

- Höhere Programmiersprache-Ebene

- Assembler-Ebene

- Betriebssystem-Ebene

- Maschinensprache-Ebene

- Mikroprogramm-Ebene

- Hardware-Ebene

- Abstraktionsebenen

## Abstraktionsebenen

#### Hardware-Ebene:

- Physikalische, elektrotechnische Ebene

- Wie ist Prozessor (i.e., Steuer- und Recheneinheiten) hardwaremäßig aufgebaut (Transistoren, Gatter, etc.)?

#### Mikroprogramm-Ebene:

- Wie werden einzelne Bausteine der Steuer- und Recheneinheit von Maschinenbefehlen angesteuert?

- Fetch–Decode–Execute

- Nur bei CISC-Architektur, bei RISC-Architektur kann diese Ebene entfallen

- Abstraktionsebenen

## Abstraktionsebenen

#### Maschinensprache-Ebene:

- Unterste f

ür Programmierer frei zug

ängliche Ebene

- Software/Hardware-Schnittstelle eines Prozessors

- Satz der verfügbaren Maschinenbefehle eines Prozessors bestimmt die "Architektur" des Rechners (CISC vs RISC)

#### Betriebssystem-Ebene:

- Verwaltung von Speicher

- Ansteuerung der Ein-/Ausgabe-Geräte

- Ausführung von Programmen

- Kommunikation zwischen Mensch und Computer

- Abstraktionsebenen

## Abstraktionsebenen

#### Assembler-Ebene:

- Stellt symbolische Notation (Mnemonics) der auf Maschinensprache- und Betriebssystem-Ebene vorhandenen Befehle zur Verfügung

- Pseudoinstruktionen, die sich einfach durch wenige Maschinenbefehle realisieren lassen

#### Höhere Programmiersprache-Ebene (Fortran, C, Java,...):

Rechner ist eine Black Box, tatsächlicher technischer Ablauf bzw. Hardware-Struktur bleiben verborgen

#### Anwendungs-Ebene:

Nur Anwendung sichtbar

Abstraktionsebenen

#### Abstraktionsebenen

VO 050041: Technische Grundlagen der Informatik

- Standard-Rechnerarchitektur

Abstraktionsebenen

# Compiler vs. Interpreter

## Programmausführung:

Jede Ebene muss auf Hardware-Ebene abgebildet werden

#### Compiler

$L_i$ -Compiler: Ein Maschinenprogramm, das ein Programm  $P_i$  der Sprache  $L_i$  in ein Programm  $P_j$  der Sprache  $L_j$  transformiert (**übersetzt**), das äquivalent zu  $P_i$  ist, d.h. das gleiche Ein-/Ausgabeverhalten wie  $P_i$  hat.

#### Interpreter

$L_i$ -Interpreter: Ein Maschinenprogramm, das ein Programm  $P_i$  der Sprache  $L_i$  Anweisung für Anweisung ausführt. Kein zu  $P_i$  äquivalentes Maschinenprogramm wird erzeugt.

- Abstraktionsebenen

# Compiler vs. Interpreter

#### Anschaulich

Wir wollen ein Rezept nachkochen, das auf französisch verfasst ist, wir verstehen diese Sprache allerdings nicht.

#### Variante 1

Mit Rezept und Wörterbuch in den Supermarkt, jede Zutat einzeln nachschauen. Zuhause jeden Arbeitsschritt einzeln nachschauen.

- Abstraktionsebenen

# Compiler vs. Interpreter

#### Anschaulich

Wir wollen ein Rezept nachkochen, das auf französisch verfasst ist, wir verstehen diese Sprache allerdings nicht.

#### Variante 1

Mit Rezept und Wörterbuch in den Supermarkt, jede Zutat einzeln nachschauen. Zuhause jeden Arbeitsschritt einzeln nachschauen. ⇒ Interpretieren

VO 050041: Technische Grundlagen der Informatik

- Standard-Rechnerarchitektur

Abstraktionsebenen

# Compiler vs. Interpreter

#### Anschaulich

Wir wollen ein Rezept nachkochen, das auf französisch verfasst ist, wir verstehen diese Sprache allerdings nicht.

#### Variante 1

Mit Rezept und Wörterbuch in den Supermarkt, jede Zutat einzeln nachschauen. Zuhause jeden Arbeitsschritt einzeln nachschauen. ⇒ Interpretieren

#### Variante 2

Das Rezept vorab von jemandem, der der Sprache mächtig ist, in eine Sprache, der wir mächtig sind, übersetzen lassen, sodann die Einkaufsliste und Befehlsliste abarbeiten. pause ⇒ Übersetzen (Kompilieren)

- Abstraktionsebenen

## Maschinenbefehlssatz

#### Maschinenbefehlssatz

- Compiler übersetzt Programm von Hochsprache in Maschinenbefehle

- Maschinenbefehlssatz: Direktes Abbild aller vom Prozessor durchführbaren Operationen → Menge der Maschinenbefehle

- Transportbefehle: Speicher-Speicher, Register-Speicher, PUSH/POP, ...

- Arithmetische Befehle: Addition, Inkrement, Dekrement, ...

- Bitweise logische Befehle: AND, OR, XOR, NOT, ...

- Schiebe- und Rotierbefehle

- Sprungbefehle ...

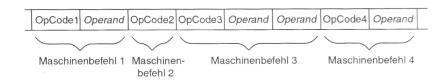

# Maschinencode / Maschinenprogramm

#### Maschinencode / Maschinenprogramm

- Programm in Maschinenbefehlsdarstellung

- Sequenz von OpCodes und Operanden

- Schwer merkbare Bitmuster

- Platzsparender: Hex-Darstellung

- Programme schwer zu lesen, unflexibel, schwer veränderlich; keine Kommentare möglich

- Assemblersprache: Jeder Maschinenbefehl durch leicht merkbare Abkürzung dargestellt, z.B. ADD, SHL, MOV, DEC, ...

— Abstraktionsebenen

# Maschinencode / Maschinenprogramm

— Abstraktionsebenen

# Maschinencode / Maschinenprogramm

#### Maschinencode / Maschinenprogramm

- Mikroprozessor kann exakt bestimmte Menge von Aktionen ausführen

- Aktion = Maschinenbefehl

- Bsp: Schreiben in Hauptspeicher, Bitmuster invertieren, ...

- Maschinenbefehl im ausführbaren Code durch Bitmuster dargestellt: Operationscode, Opcode

- Meist zusätzliche Operanden notwendig, z.B. Adresse

- **Maschinencode** = Sequenz von zusammenhängenden Maschinenbefehlen, die ablaufendes Programm darstellen

- Programm = Abfolge von Instruktionen

# Maschinencode / Maschinenprogramm

#### Ein Maschinenprogramm kann nicht mehr übersetzt werden

- Befehl für Befehl des Maschinenprogramms muss durch ein Mikroprogramm (Ebene 2) bzw. die Hardware (Ebene 1) abgearbeitet werden, d.h.

- aus dem Hauptspeicher in den Prozessor geholt,

- dekodiert, und letztendlich

- ausgeführt werden,

- ... bevor der nächste Maschinenbefehl durch den Prozessor betrachtet und verarbeitet werden kann

Abstraktionsebenen

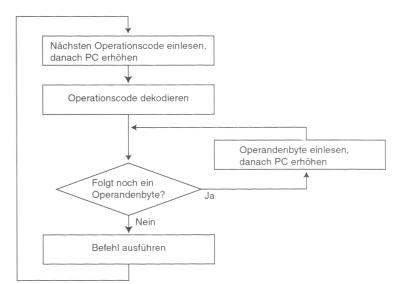

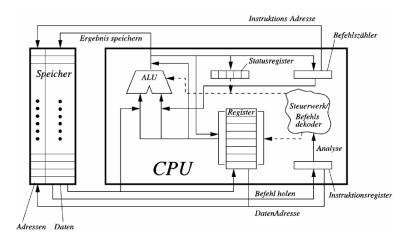

#### Fetch - Decode - Execute

#### Programmausführung

- Fetch: Nächster auszuführender Opcode wird aus Programmspeicher gelesen

- Program (auch Instruction) Counter (PC): Spezialregister, das die Adresse des nächsten Befehls enthält

- PC wird inkrementiert, zeigt damit auf nächsten Befehl

- Decode: OpCode wird bitweise mit bekannten Mustern (Befehlssatz) verglichen, um Bedeutung herauszufinden

- Falls OpCode mit Operand, wird PC inkrementiert, um Operanden auf nachfolgendem Speicherplatz zu lesen (bis alle Operanden gelesen)

- Execute: OpCode wird ausgeführt;

Abstraktionsebenen

#### Fetch - Decode - Execute

- Prozessor

## Der Prozessor

#### ...auch bekannt als

- Central Processing Unit, Central Processor Unit (CPU)

- Hauptprozessor

- Mikroprozessor

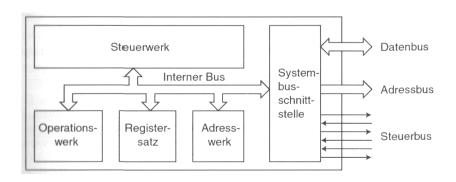

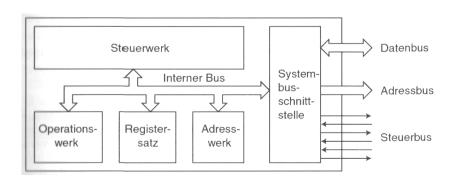

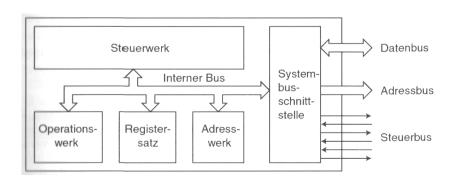

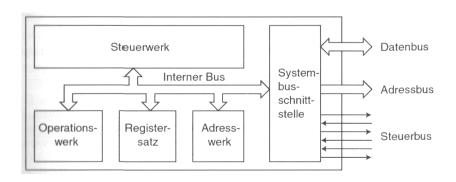

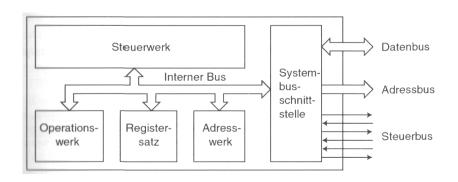

## Interner Aufbau

#### Interner Aufbau einer CPU

- Registersatz: Register, um Daten innerhalb des Prozessors speichern zu können

- Steuerwerk: Verantwortlich für Ablaufsteuerung

- Operationswerk (Rechenwerk): Eigentliche Datenverarbeitung

- Adresswerk: Um auf Daten und Code im Hauptspeicher zugreifen zu können

- Systembus-Schnittstelle: Datenverkehr mit Rest des Systems

Prozessor

## Schematisch

- Prozessor

# Registersatz

#### Register

- Ein Speicherbereich innerhalb eines Prozessors

- Durch internen Datenbus meist direkt mit ALU verbunden

- Wesentlich schneller (und kleiner) als Hauptspeicher

- Gruppe von Flip-Flops mit gemeinsamer Steuerung

- 1 Flip-Flop kann 1 Bit speichern

- Register haben gewissen Breite, meist 8, 16, 32, 64... Bit

- Registersatz: Nach außen "sichtbare" Register

# Registersatz

#### Registertypen

- Datenregister (Akkumulator): Speichern Operanden für die ALU und deren Resultate

- Adressregister: Speichern Speicheradressen eines Operanden oder Befehls

- Universalregister: Für verschiedene Inhalte verwendbar

- Spezialregister: Für bestimmte Zwecke vorgesehen

- Befehlszählregister: Speicheradresse des nächsten auszuführenden Befehls

- Befehlsregister (Instruction register):

(Zwischen)-Speicherung des aktuellen Befehls

- Statusregister: z.B. Auftreten eines Überlaufs

Prozessor

## Schematisch

-Prozessor

## Steuerwerk

#### Steuerwerk - Control Unit (CU)

- Steuert den Ablauf der Befehlsverarbeitung

- Decodierung der OpCodes (Instruction Decoder)

- Ansteuerung und Koordination der anderen Elemente

- Opcode wird im Befehlsregister abgelegt und dekodiert

- Mittels Schaltwerk werden notwendige Signale für Ausführung erzeugt

- Prozessor

## Steuerwerk: Beispiel (siehe K. Wüst, Mikroprozessortechnik, 4. Auflage)

# Programmzähler zeigt auf Speicherplatz, an dem folgender OpCode liegt: Kopiere Register 1 in Register 2

- Programmzähler auf Adressbus legen

- Aktivierung ext. Steuerleitungen f. Lesezugriff im Speicher

- Einspeicherimpuls für Befehlsregister erzeugen, OpCode vom Datenbus entnehmen und im Befehlsregister einspeichern

- Dekodierung des Opcodes

- Register 1 auf Senden einstellen und auf internen Datenbus aufschalten

- Register 2 auf internen Datenbus aufschalten

- Einspeicherimpuls an Register 2 geben

- Programmzähler inkrementieren

- Prozessor

## Steuerwerk: Beispiel

#### Zu beachten

- Wartezeiten + Buszugriffe in Ausführungsphase

- Komplizierte Sequenzen von Signale zu erzeugen!

- Exakter zeitlicher Ablauf ⇒ Synchronisierung!

- Statusflags von Prozessor zu berücksichtigen

- Externe Signale, z.B. Unterbrechungen (Interrupts)

- •

Prozessor

## Schematisch

- Prozessor

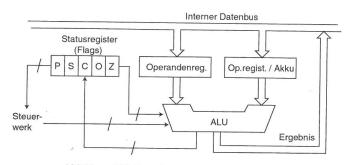

# Operationswerk

## Operations-/Rechenwerk, Arithmetic & Logic Unit (ALU)

- Führt die vom Steuerwerk verlangten logischen und arithmetischen Operationen aus

- Wird vom Steuerwerk nach Dekodierung einer entsprechenden Instruktion angesprochen

Prozessor

# Operationswerk

#### Operations-/Rechenwerk, Arithmetic & Logic Unit (ALU)

- Führt die vom Steuerwerk verlangten logischen und arithmetischen Operationen aus

- Wird vom Steuerwerk nach Dekodierung einer entsprechenden Instruktion angesprochen

- Verfügbare Operationen unterschiedlich, z.B.:

- a ∧ b

- ¬b

- a + b

- a+1

- a − b

- bit shift left/right

• . . .

Zum Ausprobieren: http://tams-www.informatik.uni-hamburg.de/research/software/applets/hades/webdemos/20-arithmetic/50-74181/SN74181.html

# Operationswerk

## Operations-/Rechenwerk, Arithmetic & Logic Unit (ALU)

- Über Steuereingänge auf bestimmte Anzahl von arithmetisch/logischen Operationen einstellbar

- Hängt vom Befehl ab, wird vom Steuerwerk nach dem OpCode-Decode gemacht

- Schaltwerk ohne eigene Speicherzellen:

Operandenregister (Hilfsregister) auf Dateneingänge für Zeit der Berechnung aufgeschaltet

- Ergebnis wird über Datenbus z.B. in Universalregister geschrieben

- Kann aber auch erneut in Operandenregister geladen werden ⇒ komplexe Operationen in mehreren Schritten ausführen

Prozessor

# Operationswerk

Abbildung 7.8: Zentraler Teil des Operationswerkes.

K. Wüst, Mikroprozessortechnik, 4. Auflage

Prozessor

## Schematisch

- Prozessor

## Adresswerk

#### Aufgaben

Berechnet nach den Vorschriften des Steuerwerks die Adresse eines Befehls oder eines Operanden

#### Adressierungsarten

- Unmittelbare Adressierung: Operand als Konstante im Befehl enthalten (folgt unmittelbar auf den OpCode)

- Registeradressierung: Register direkt angesprochen

-Prozessor

## Adresswerk

#### Adressierungsarten

- Direkte Adressierung: Speicheradresse beim Kompilieren bekannt und als Operand im Maschinencode

- Z.B. Sortieralgorithmen: Adressen müssen zur Laufzeit festlegbar sein

- Register-indirekte Addressierung: Inhalt eines Registers als Adresse interpretiert

- Basisregister: Volle Adressbusbreite, für Anfangsadresse

- Displacement (aus Maschinencode) kann addiert werden

- Adresswerk hat eigenen Adressrechner

-Prozessor

## Adresswerk

#### Adressierungsarten

- Indexregister: Kann z.B. Autoinkrement, Autodekrement

- Für indizierte Adressierung ideal, um zusammenhängende Datenblöcke sequenziell zu adressieren

- Speicherindirekte Adressierung: Register verweist auf Speicherplatz, diese wird gelesen und als Adresse verwendet

- · Bis zu zwei Displacements möglich

- Prozessor

## Adresswerk

#### Stackpointer

- Spezialregister, SP, Stapelzeiger

- Verwendung eines Stacks in Hardware unterstützt

- Speicherstruktur mit Last-In–First-Out Prinzip (LIFO)

- Anschaulich: ein Stapel Teller oder Bücher, ...

- · Temporäre Daten, z.B. Programmverlauf

- Wächst meist zu kleineren Speicheradressen hin

- Neues Wort im Stack ablegen: Stackpointer dekrementieren (PUSH)

- Wort von Stack holen: Stackpointer inkrementieren (POP)

- Standard-Rechnerarchitektur

Prozessor

#### Schematisch

### Systembusschnittstelle

#### Systembus (!= interner CPU Bus)

- Adressleitungen (Adressbus): unidirektional, Prozessor immer Sender

- Adressbus-Breite gibt adressierbaren Bereich an

- 32 bit  $\Rightarrow$  2<sup>32</sup> · 1 Byte = 4096 MiB = 4 GiB (386 bis Pentium)

- 48 bit ⇒ 2<sup>48</sup> · 1 Byte = 256 TiB (AMD64)

...wenn an jeder Adresse 1 Byte gespeichert wird.

- Datenleitungen (Datenbus): bidirektional

- Datenbus-Breite: Wie viele Daten k\u00f6nnen in einem Schritt transferiert werden

- Steuerleitungen (Steuerbus): Jede Leitung hat eine andere Aufgabe

- Standard-Rechnerarchitektur

Prozessor

# The Big Picture

Sehenswert: http://www.youtube.com/watch?v=cNN\_tTXABUA

- Standard-Rechnerarchitektur

- Prozessor

### **ISA**

#### ISA - Instruction Set Architecture / Befehlssatz

- Gesamte nach außen hin sichtbare Architektur

- 1 Befehlssatz (s.o.)

- 2 Registersatz (s.o.)

- 3 Speichermodell (Größe des Adressraums, Breite der Busse, etc.)

- Muss zur Erstellung von Maschinenprogrammen für diesen Prozessor bekannt sein

- Für Assemblerprogrammierung, Aufbau von Compilern, ...

- ISA = Schnittstelle zwischen Hard- und Software

Standard-Rechnerarchitektur

Prozessor

### **ISA**

### Überblick

- Einführung und Formale Aspekt Klassifikation

Design und Performance

Quantitative Methoden

- 2 Standard-Rechnerarchitektur Abstraktionsebenen Prozessor

- Speicherverwaltung Virtueller Speicher und Paging Caching

- 4 Externer Speicher Festplatten Disk Scheduling

- Skalare und superskalare/parallele Architekturer CISC und RISC Pipelining Superskalare Architekturen

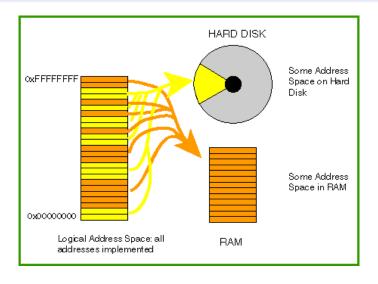

└Virtueller Speicher und Paging

## Virtueller Speicher

- Früher: Overlays, Programmteile manuell ausgelagert

- Probleme: Manuell, ist f

ür jede Maschine anders

└Virtueller Speicher und Paging

## Virtueller Speicher

- Früher: Overlays, Programmteile manuell ausgelagert

- Probleme: Manuell, ist f

ür jede Maschine anders

- Virtueller (logischer) Adressraum: unabhängig vom physikalisch vorhandenen Arbeitsspeicher

└Virtueller Speicher und Paging

## Virtueller Speicher

- Früher: Overlays, Programmteile manuell ausgelagert

- Probleme: Manuell, ist f

ür jede Maschine anders

- Virtueller (logischer) Adressraum: unabhängig vom physikalisch vorhandenen Arbeitsspeicher

- Betriebssystem lagert bei Speichermangel Bereiche (Pages) auf Massenspeicher aus (Paging, Swapping)

└Virtueller Speicher und Paging

## Virtueller Speicher

- Früher: Overlays, Programmteile manuell ausgelagert

- Probleme: Manuell, ist f

ür jede Maschine anders

- Virtueller (logischer) Adressraum: unabhängig vom physikalisch vorhandenen Arbeitsspeicher

- Betriebssystem lagert bei Speichermangel Bereiche (Pages) auf Massenspeicher aus (Paging, Swapping)

- Paging ist transparent für Programmierer (muss keine Rücksicht nehmen, ob Adressen im real vorhandenen physikalischen Arbeitsspeicher wirklich existieren)

└Virtueller Speicher und Paging

### Virtueller Speicher

- Früher: Overlays, Programmteile manuell ausgelagert

- Probleme: Manuell, ist f

ür jede Maschine anders

- Virtueller (logischer) Adressraum: unabhängig vom physikalisch vorhandenen Arbeitsspeicher

- Betriebssystem lagert bei Speichermangel Bereiche (Pages) auf Massenspeicher aus (Paging, Swapping)

- Paging ist transparent für Programmierer (muss keine Rücksicht nehmen, ob Adressen im real vorhandenen physikalischen Arbeitsspeicher wirklich existieren)

- Virtuelle Adresse ⇒ physikalische Adresse

- Hardware-Baustein: Memory Management Unit auf CPU

└Virtueller Speicher und Paging

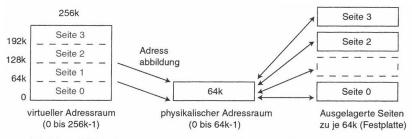

## Virtueller Speicher

Abbildung 10.1: Die Seitenauslagerung ermöglicht einen beliebig großen virtuellen Adressraum. In diesem Beispiel befindet sich gerade Seite 1 im physikalischen Speicher, die anderen Seiten sind ausgelagert.

K. Wüst, Mikroprozessortechnik, 4. Auflage

└ Virtueller Speicher und Paging

## Virtueller Speicher

└ Virtueller Speicher und Paging

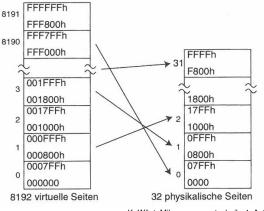

### Virtueller Speicher – Beispiel

Abbildung 10.2: Beispiel zum Paging: Ein virtueller Adressraum von 16 MByte, wird mit einer Seitengröße von 2 KByte auf einem physikalischen Adressraum von 64 KByte abgebildet.

K. Wüst, Mikroprozessortechnik, 4. Auflage

VO 050041: Technische Grundlagen der Informatik

Speicherverwaltung

└Virtueller Speicher und Paging

# **Paging**

Page size: 512 Byte bis 4 MiB, typisch sind 4 KiB

Virtueller Speicher und Paging

# **Paging**

#### Page size: 512 Byte bis 4 MiB, typisch sind 4 KiB

⇒ zu groß: Ein-/Auslagerung dauert zu lange

└Virtueller Speicher und Paging

## **Paging**

#### Page size: 512 Byte bis 4 MiB, typisch sind 4 KiB

⇒ zu groß: Ein-/Auslagerung dauert zu lange

⇒ zu klein: HDD Seek Time problematisch

Virtueller Speicher und Paging

# **Paging**

#### Page size: 512 Byte bis 4 MiB, typisch sind 4 KiB

⇒ zu groß: Ein-/Auslagerung dauert zu lange

⇒ zu klein: HDD Seek Time problematisch

Page table: Verwaltung der Pages

Virtueller Speicher und Paging

## **Paging**

#### Page size: 512 Byte bis 4 MiB, typisch sind 4 KiB

⇒ zu groß: Ein-/Auslagerung dauert zu lange

⇒ zu klein: HDD Seek Time problematisch

Page table: Verwaltung der Pages

Page fault: Page wird gebraucht, wurde aber ausgelagert

└Virtueller Speicher und Paging

# **Paging**

#### Page size: 512 Byte bis 4 MiB, typisch sind 4 KiB

- ⇒ zu groß: Ein-/Auslagerung dauert zu lange

- ⇒ zu klein: HDD Seek Time problematisch

- Page table: Verwaltung der Pages

- Page fault: Page wird gebraucht, wurde aber ausgelagert

- Demand paging: Physikalischer Speicher wird sukzessive mit benötigten Speicherbereichen befüllt (per page faults).

Liefert nach einiger Zeit working set (Arbeitsmenge) des Programms.

└Virtueller Speicher und Paging

## **Paging**

#### Page size: 512 Byte bis 4 MiB, typisch sind 4 KiB

- ⇒ zu groß: Ein-/Auslagerung dauert zu lange

- ⇒ zu klein: HDD Seek Time problematisch

- Page table: Verwaltung der Pages

- Page fault: Page wird gebraucht, wurde aber ausgelagert

- Demand paging: Physikalischer Speicher wird sukzessive mit benötigten Speicherbereichen befüllt (per page faults). Liefert nach einiger Zeit working set (Arbeitsmenge) des Programms.

- Dirty bit: Wurde eine Seite überhaupt geändert, oder muss sie bei Auslagerung gar nicht auf die Disk zurückgeschrieben werden?

Virtueller Speicher und Paging

## **Paging**

#### Was passiert wenn physikalischer Speicher voll ist?

- Wenn physikalischer Speicher voll ist, muss vor dem Einlagern einer angeforderten Page (Page-In) eine andere Page ausgelagert (Page-out) werden. <u>Welche</u>?

- Diejenige, die möglichst lange nicht mehr gebraucht wird

└Virtueller Speicher und Paging

# **Paging**

#### Was passiert wenn physikalischer Speicher voll ist?

- Wenn physikalischer Speicher voll ist, muss vor dem Einlagern einer angeforderten Page (Page-In) eine andere Page ausgelagert (Page-out) werden. <u>Welche</u>?

- Diejenige, die möglichst lange nicht mehr gebraucht wird

- Lässt sich aber nur per Wahrscheinlichkeit ausdrücken:

- LRU-Ersetzung: die am längsten nicht gebraucht wurde

- LFU-Ersetzung: die am seltensten gebraucht wurde

- FIFO-Ersetzung: die am längsten im Speicher ist

└Virtueller Speicher und Paging

# **Paging**

#### Was passiert wenn physikalischer Speicher voll ist?

- Wenn physikalischer Speicher voll ist, muss vor dem Einlagern einer angeforderten Page (Page-In) eine andere Page ausgelagert (Page-out) werden. <u>Welche</u>?

- Diejenige, die möglichst lange nicht mehr gebraucht wird

- Lässt sich aber nur per Wahrscheinlichkeit ausdrücken:

- LRU-Ersetzung: die am längsten nicht gebraucht wurde

- LFU-Ersetzung: die am seltensten gebraucht wurde

- FIFO-Ersetzung: die am längsten im Speicher ist

- Thrashing: System ist (fast) nur mit Einlagerung und Auslagerung beschäftigt und kann kaum (gar nicht) Programm abarbeiten

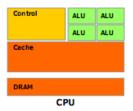

#### Warum Caches?

#### Motivation

- CPUs in letzten 30 Jahren um Größenordnungen schneller

- (Haupt-)Speicher auch schneller, aber nicht in diesem

Maße ⇒ Speicherzugriff dauert oft mehr als 10 CPU-Takte

- CPU-Designziel: in jedem Takt Befehl abarbeiten

- Bei superskalaren CPUs sogar noch mehr Befehle/Takt

- Daten und Code müssen schnell genug aus Speicher geliefert werden, sonst sind alle CPU-Fortschritte sinnlos!

- ⇒ Speicher-Latenzzeit: Wartezeit, bis Speicherzugriff anläuft

- ⇒ Speicherbandbreite: Übertragungsrate

- ... müssen beide verbessert werden

- ⇒ Caches: kleine, schnelle Zwischenspeicher

Caching

## **CPU Memory Gap**

-Caching

## Lokalitätsprinzip

#### Auf (Haupt-)Speicher wird meist nicht völlig zufällig zugegriffen

- Räumliche Lokalität: Häufig Zugriffe auf Adressen, die in der Nähe kürzlich benutzter Adressen liegen

- 2 Zeitliche Lokalität: Folgezugriffe auf kürzliche benutzte Adressen

- → Kürzlich benutzte Daten möglichst lange im Cache halten

- Nach Hauptspeicherzugriff wird nicht nur Inhalt der adressierten Speicherzelle im Cache aufbewahrt (zeitliche Lokalität), sondern gleich ganzer Speicherblock (räumliche Lokalität), in dem die Speicherzelle liegt

Caching

### Cache Hits, Cache Misses

#### "Datum": Eine kleine Datenmenge im Cache

- Cache zunächst leer, füllt sich bei Zugriffen: Kopie des Speicherblocks wird im Cache abgelegt

- Lesezugriff auf Hauptspeicher: Cache auf Kopie prüfen

### Cache Hits, Cache Misses

#### "Datum": Eine kleine Datenmenge im Cache

- Cache zunächst leer, füllt sich bei Zugriffen: Kopie des Speicherblocks wird im Cache abgelegt

- Lesezugriff auf Hauptspeicher: Cache auf Kopie prüfen

- · Cache-Hit: Datum vorhanden, lesen aus Cache

-Caching

### Cache Hits, Cache Misses

#### "Datum": Eine kleine Datenmenge im Cache

- Cache zunächst leer, füllt sich bei Zugriffen: Kopie des Speicherblocks wird im Cache abgelegt

- Lesezugriff auf Hauptspeicher: Cache auf Kopie prüfen

- Cache-Hit: Datum vorhanden, lesen aus Cache

- Cache-Miss: Datum nicht vorhanden, lesen aus Hauptspeicher – mehrfacher Aufwand

- Hit-Rate: Wahrscheinlichkeit für Cache Hit

-Caching

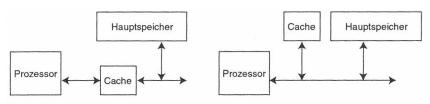

## Look-Through-Cache vs. Look-aside-Cache

Abbildung 10.8: Ein Cache kann zwischen Hauptspeicher und Prozessor liegen (Look-Through-Cache, links) oder parallel zum Hauptspeicher (Look-aside-Cache, rechts).

K. Wüst, Mikroprozessortechnik, 4. Auflage

-Caching

Speicherverwaltung

## Look-Through-Cache vs. Look-Aside-Cache

#### Look-Through-Cache

- Zwischen CPU und Hauptspeicher

- Schnell an CPU angebunden (höherer Bustakt als Hauptspeicher)

- Cache und Hauptspeicher nicht gleichzeitig aktivierbar (Hauptspeicherzugriff erfolgt erst, wenn Daten im Cache nicht gefunden wurden)

- ⇒ Bei guter Hit-Rate fast nur Zugriffszeit des Caches entscheidend

- ⇒ Bei schlechter Hit-Rate hohe Wartezeiten

-Caching

# Look-Through-Cache vs. Look-Aside-Cache

#### Look-Aside-Cache

- Parallel zum Hauptspeicher

- Cache-Zugriff und Hauptspeicher-Zugriff werden gleichzeitig aktiviert

- ⇒ Kein Zeitverlust bei Fehltreffer im Cache

- ⇒ Aber: Cache wird durch langsamen Speicherbus getaktet

-Caching

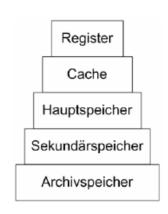

## Speicherhierarchie

"Ideally one would desire an indefinitely large memory capacity such that any particular word would be immediately available. We are forced to recognize the possibility of constructing a hierarchy of memories, each of which has greater capacity than the preceding one but which is less quickly accessible."

- A.W.Burks, H.H. Goldstine and J. von Neumann (1946)

VO 050041: Technische Grundlagen der Informatik

Speicherverwaltung

Caching

## Mehrstufige Caches

Einstufige Caches oft ineffizient ⇒ mehrstufige Caches

-Caching

## Mehrstufige Caches

#### Einstufige Caches oft ineffizient ⇒ mehrstufige Caches

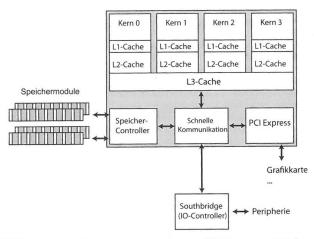

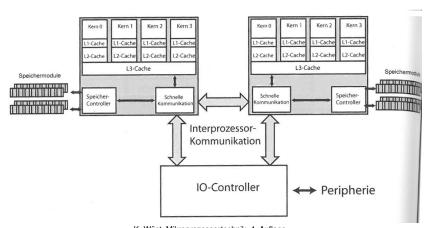

- 1 First-Level (L1) Cache:

- Kleiner Cache, mit CPU-Takt betrieben; ca. 16-64 KiB

- Meist in Prozessorchip integriert

- Split cache: Daten / Code; gleichzeitiger Zugriff möglich

-Speicherverwaltung

-Caching

# Mehrstufige Caches

### Einstufige Caches oft ineffizient ⇒ mehrstufige Caches

- 1 First-Level (L1) Cache:

- Kleiner Cache, mit CPU-Takt betrieben; ca. 16-64 KiB

- Meist in Prozessorchip integriert

- Split cache: Daten / Code; gleichzeitiger Zugriff möglich

### 2 L2-Cache

- Hinter L1-Cache; f<CPU-Takt; ca. 256-512 KiB</li>

- · Meist in Prozessorchip integriert

- Unified cache: Daten und Code gemeinsam

## Mehrstufige Caches

### Einstufige Caches oft ineffizient ⇒ mehrstufige Caches

- 1 First-Level (L1) Cache:

- Kleiner Cache, mit CPU-Takt betrieben; ca. 16-64 KiB

- Meist in Prozessorchip integriert

- Split cache: Daten / Code; gleichzeitiger Zugriff möglich

- 2 L2-Cache

- Hinter L1-Cache; f<CPU-Takt; ca. 256-512 KiB</li>

- Meist in Prozessorchip integriert

- Unified cache: Daten und Code gemeinsam

- 3 L3-Cache

- Hinter L2-Cache; oft schnelles SRAM auf Systemplatine

- Bei MultiCore-CPUs meist geteilt zwischen einzelnen Cores (L1 und L2 extra für jeden Core)

Speicherverwaltung

## Mehrstufige Caches

### Einstufige Caches oft ineffizient ⇒ mehrstufige Caches

- 1 First-Level (L1) Cache:

- Kleiner Cache, mit CPU-Takt betrieben; ca. 16-64 KiB

- Meist in Prozessorchip integriert

- Split cache: Daten / Code; gleichzeitiger Zugriff möglich

- 2 L2-Cache

- Hinter L1-Cache; f<CPU-Takt; ca. 256-512 KiB</li>

- Meist in Prozessorchip integriert

- Unified cache: Daten und Code gemeinsam

- 3 L3-Cache

- Hinter L2-Cache; oft schnelles SRAM auf Systemplatine

- Bei MultiCore-CPUs meist geteilt zwischen einzelnen Cores (L1 und L2 extra für jeden Core)

- 4 L4-Cache Prinzip: Hauptspeicher als Cache für HDD ...

# Memory Stall Cycles, Miss Penalty

### MSC, MP

- Memory Stall Cycles (MSC): Anzahl der Zyklen, die CPU auf Speicherzugriff warten muss

- Hängt von der Anzahl der Cache Misses und den Kosten pro Cache Miss (Miss Penalty) ab

- MSC = Anzahl der Misses · MP

- =  $IC \cdot MPI \cdot MP = IC \cdot \frac{Misses}{Instruktion} \cdot MP$

# Memory Stall Cycles, Miss Penalty

### MSC, MP

□ Caching

- Memory Stall Cycles (MSC): Anzahl der Zyklen, die CPU auf Speicherzugriff warten muss

- Hängt von der Anzahl der Cache Misses und den Kosten pro Cache Miss (Miss Penalty) ab

- MSC = Anzahl der Misses · MP

- =  $IC \cdot MPI \cdot MP = IC \cdot \frac{Misses}{Instruktion} \cdot MP$

- ullet = IC  $\cdot$   $\frac{\textit{Speicherzugriff}}{\textit{Instruktion}} \cdot \frac{\textit{Misses}}{\textit{Speicherzugriff}} \cdot \textit{MP}$

# Memory Stall Cycles, Miss Penalty

### MSC, MP

- Memory Stall Cycles (MSC): Anzahl der Zyklen, die CPU auf Speicherzugriff warten muss

- Hängt von der Anzahl der Cache Misses und den Kosten pro Cache Miss (Miss Penalty) ab

- MSC = Anzahl der Misses · MP

• =

$$IC \cdot MPI \cdot MP = IC \cdot \frac{Misses}{Instruktion} \cdot MP$$

$$ullet$$

= IC  $\cdot$   $\frac{Speicherzugriff}{Instruktion}$   $\cdot$   $\frac{Misses}{Speicherzugriff}$   $\cdot$  MP

•

$$MPI = \frac{Misses}{Instruktion} = \frac{Speicherzugriffe}{Instruktion} \cdot MR$$

# Memory Stall Cycles, Miss Penalty

### MSC, MP

- Memory Stall Cycles (MSC): Anzahl der Zyklen, die CPU auf Speicherzugriff warten muss

- Hängt von der Anzahl der Cache Misses und den Kosten pro Cache Miss (Miss Penalty) ab

- MSC = Anzahl der Misses · MP

- =  $IC \cdot MPI \cdot MP = IC \cdot \frac{Misses}{Instruktion} \cdot MP$

- ullet = IC  $\cdot$   $\frac{Speicherzugriff}{Instruktion}$   $\cdot$   $\frac{Misses}{Speicherzugriff}$   $\cdot$  MP

- $MPI = \frac{\textit{Misses}}{\textit{Instruktion}} = \frac{\textit{Speicherzugriffe}}{\textit{Instruktion}} \cdot \textit{MR}$

- $MR = \frac{\textit{Misses}}{\textit{Speicherzugriff}}$  (Miss Rate)

└- Caching

## Performance

### Mittlere Speicherzugriffszeit

- $\bar{t}_{SZ} = t_H + MR \cdot MP$

- *t<sub>H</sub>* . . . Hit time, Zeit um Treffer im Cache zu erzielen

- MR... Miss rate, Wahrscheinlichkeit für Cache Miss

- MP... Extra-Aufwand bei Cache Miss (zB L2, RAM, ..)

## Performance

### Mittlere Speicherzugriffszeit

- $\bar{t}_{SZ} = t_H + MR \cdot MP$

- t<sub>H</sub>... Hit time, Zeit um Treffer im Cache zu erzielen

- MR... Miss rate, Wahrscheinlichkeit für Cache Miss

- MP... Extra-Aufwand bei Cache Miss (zB L2, RAM, ..)

### Für mehrstufige Caches

- $\bar{t}_{SZ} = t_{H,L1} + MR_{L1} \cdot MP_{L1}$

- $MP_{L1} = t_{H,L2} + MR_{L2} \cdot MP_{L2}$

- $\bar{t}_{SZ} = t_{H,L1} + MR_{L1} \cdot (t_{H,L2} + MR_{L2} \cdot MP_{L2})$

## Performance

Caching

## Average Memory Stalls per Intruction (AMSPI)

- Durchschnittliche Anzahl an Zyklen pro Instruktion, in denen auf Daten aus dem Speicher gewartet wird

- Annahme: L1-Cache wird mit vollem Prozessortakt betrieben ⇒ erfolgreicher L1-Cache Zugriff braucht also keinen Extra-Takt (Zyklus)

- $AMSPI = MPI_{L1} \cdot t_{H,L2} + MPI_{L2} \cdot MP_{L2}$

## Cache-Optimierungen

### Grob: 3 Varianten

- Miss Penalty (MP) senken

- Mehrstufige Caches

# Cache-Optimierungen

### Grob: 3 Varianten

- 1 Miss Penalty (MP) senken

- Mehrstufige Caches

- 2 Miss Rate (MR) senken

- Blockgröße erhöhen, nutzt räumliche Lokalität, erhöht MP

Speicherverwaltung

-Caching

# Cache-Optimierungen

### Grob: 3 Varianten

- 1 Miss Penalty (MP) senken

- Mehrstufige Caches

- Miss Rate (MR) senken

- Blockgröße erhöhen, nutzt räumliche Lokalität, erhöht MP

- 3 Hit Time (HT) senken

- Kleiner, einfacher, schneller Cache; On-chip, CPU-Takt, direct mapped

Speicherverwaltung

-Caching

## Cache-Organisation

### Bestandteile eines Caches

- 1 Datenbereich

- Besteht aus Anzahl von Cache-Zeilen (Cache Lines)

- Alle Lines haben einheitliche Blocklänge (block/line size)

- Immer ganze Cache Line laden/ersetzen

-Speicherverwaltung

-Caching

# Cache-Organisation

### Bestandteile eines Caches

- 1 Datenbereich

- Besteht aus Anzahl von Cache-Zeilen (Cache Lines)

- Alle Lines haben einheitliche Blocklänge (block/line size)

- Immer ganze Cache Line laden/ersetzen

- 2 Identifikationsbereich

- Enthält tags (Etikett): Aus welchem Abschnitt des Hauptspeichers wurde Cache-Zeile geladen

- · Stellt fest ob ein Datum im Cache ist oder nicht

Speicherverwaltung

-Caching

# Cache-Organisation

### Bestandteile eines Caches

- 1 Datenbereich

- Besteht aus Anzahl von Cache-Zeilen (Cache Lines)

- Alle Lines haben einheitliche Blocklänge (block/line size)

- Immer ganze Cache Line laden/ersetzen

- 2 Identifikationsbereich

- Enthält tags (Etikett): Aus welchem Abschnitt des Hauptspeichers wurde Cache-Zeile geladen

- · Stellt fest ob ein Datum im Cache ist oder nicht

- 3 Verwaltungsbereich: Mindestens zwei Bits

- Valid bit: Ist Cache-Line ungültig (veraltet, 0) oder gültig (1)

- Dirty bit: Wurde auf Cache-Line geschrieben (1) oder nicht

(0) für Copy-Back-Ersetzungsstrategie wichtig

Cache-Organisation

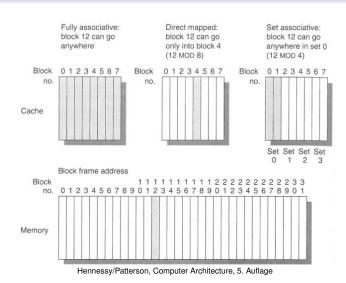

## Mögliche Organisationsformen

Vollassoziativ (fully associative)

# Cache-Organisation

## Mögliche Organisationsformen

- 1 Vollassoziativ (fully associative)

- 2 Direkt abbildend (direct mapped)

# Cache-Organisation

## Mögliche Organisationsformen

- **1 Vollassoziativ** (fully associative)

- 2 Direkt abbildend (direct mapped)

- Mehrfach assoziativer Cache (n-way set associative, teilassoziativ), am häufigsten zu finden

# Fully associative

## Fully associative

Datenblock in beliebiger Cache-Zeile abspeicherbar

# Fully associative

### Fully associative

- Datenblock in beliebiger Cache-Zeile abspeicherbar

- Alle Tags mit angefragter Adresse zu vergleichen

- Muss aus Performance-Gründen gleichzeitig erfolgen

# Fully associative

### Fully associative

- Datenblock in beliebiger Cache-Zeile abspeicherbar

- ⇒ Alle Tags mit angefragter Adresse zu vergleichen

- Muss aus Performance-Gründen gleichzeitig erfolgen

- ⇒ Vergleichereinheit für jede Cache-Zeile

- ⇒ Sehr hoher Hardwareaufwand

# Fully associative

### Fully associative

- Datenblock in beliebiger Cache-Zeile abspeicherbar

- ⇒ Alle Tags mit angefragter Adresse zu vergleichen

- Muss aus Performance-Gründen gleichzeitig erfolgen

- ⇒ Vergleichereinheit für jede Cache-Zeile

- ⇒ Sehr hoher Hardwareaufwand

- Dafür keine Einschränkungen bei Ersetzung!

- ⇒ Höchste Trefferquote aller Organisationen

# Direct mapped

## Direct mapped

Teil der Speicheradresse wird als Index benutzt um dem Datenblock eine Cache-Zeile zuzuordnen.

# Direct mapped

### Direct mapped

- Teil der Speicheradresse wird als Index benutzt um dem Datenblock eine Cache-Zeile zuzuordnen.

- ⇒ Block kann <u>nur</u> dort gespeichert werden

- ⇒ Es gibt keine Ersetzungsstrategie

# Direct mapped

### Direct mapped

- Teil der Speicheradresse wird als Index benutzt um dem Datenblock eine Cache-Zeile zuzuordnen.

- ⇒ Block kann nur dort gespeichert werden

- ⇒ Es gibt keine Ersetzungsstrategie

- Kann zu Thrashing führen = schlechter als gar kein Cache

# Direct mapped

### Direct mapped

- Teil der Speicheradresse wird als Index benutzt um dem Datenblock eine Cache-Zeile zuzuordnen.

- ⇒ Block kann <u>nur</u> dort gespeichert werden

- ⇒ Es gibt keine Ersetzungsstrategie

- Kann zu Thrashing führen = schlechter als gar kein Cache

- Aus Index sofort klar, wo Block stehen muss (falls im Cache)

- Einfacher Aufbau, nur ein Vergleicher notwendig

- ⇒ Schlechteste Trefferquote aller Organisationen

## n-way set associative

#### n-way set associative

- Kompromiss zw. fully associativ und direct mapped

- Cache-Zeilen werden zu einem Satz zusammengefasst

- Satznummer wird als Index benutzt:

## n-way set associative

### n-way set associative

- Kompromiss zw. fully associativ und direct mapped

- Cache-Zeilen werden zu einem Satz zusammengefasst

- Satznummer wird als Index benutzt:

- Aus Adresse ergibt sich nur Nummer des Satzes

- Innerhalb des Satzes kann frei gewählt werden

- Ersetzungsstrategien möglich

- Trefferbestimmung:

## n-way set associative

#### n-way set associative

- Kompromiss zw. fully associativ und direct mapped

- Cache-Zeilen werden zu einem Satz zusammengefasst

- Satznummer wird als Index benutzt:

- Aus Adresse ergibt sich nur Nummer des Satzes

- Innerhalb des Satzes kann frei gewählt werden

- Ersetzungsstrategien möglich

- Trefferbestimmung:

- Index verweist auf Satz, wo Datum stehen könnte

- Innerhalb von Satz kann Datum in n Einträgen liegen

- n Vergleicher: parallel Tags der n Einträge vergleichen

- Speicherverwaltung

-Caching

# Cache Organisationen im Überblick

Speicherverwaltung

# Cache Organisationen – Beispiel

#### AMD K<sub>10</sub>

- 1 L1

- 64 KB 2-way set associative instruction cache

- 64 KB 2-way set associative data cache

- 2 512 KB 16-way set associative cache

- 3 32-way set associative L3 shared cache

- Speicherverwaltung

-Caching

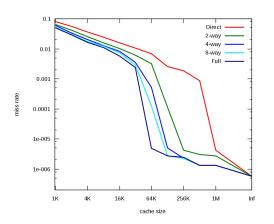

# Vergleich per Benchmark

Abbildung: Miss rate versus cache size on Integer portion of SPEC CPU2000 –http://en.wikipedia.org/wiki/File:Cache,missrate.png

# Ersetzungsstrategien

### Ersetzungsstrategien

- Analog zu virtuellem Speicher

- LRU, LFU, FIFO, ...

- Random: Zufallsprinzip → erstaunlich gute Ergebnisse

# Aktualisierungsstrategien

### Wichtige Begriffe

• Konsistenz: Alle Kopien eines Datums inhaltsgleich

## Aktualisierungsstrategien

### Wichtige Begriffe

- Konsistenz: Alle Kopien eines Datums inhaltsgleich

- Kohärenz: Korrektes Fortschreiten des Systemzustands

- Inkohärenz, wenn Dateninkonsistenz nicht bereinigt wird

- Lesen vs. Schreiben

#### Lesen

Caching

Lese-Treffer: Daten zeitsparend aus Cache nehmen; keine weiteren Aktionen -Caching

# Aktualisierungsstrategien

#### Wichtige Begriffe

- Konsistenz: Alle Kopien eines Datums inhaltsgleich

- Kohärenz: Korrektes Fortschreiten des Systemzustands

- Inkohärenz, wenn Dateninkonsistenz nicht bereinigt wird

- Lesen vs. Schreiben

#### Lesen

- Lese-Treffer: Daten zeitsparend aus Cache nehmen; keine weiteren Aktionen

- Lese-Fehltreffer: Block, der Datum enthält, in Cache laden; angefordertes Datum in CPU laden

# Aktualisierungsstrategien: Schreiben

#### Schreib-Treffer

Zwei Möglichkeiten:

1 Write-Trough-Strategie: Datum wird in Cache und in Hauptspeicher geschrieben: Einfach, garantiert Konsistenz

-Caching

# Aktualisierungsstrategien: Schreiben

#### Schreib-Treffer

Zwei Möglichkeiten:

- Write-Trough-Strategie: Datum wird in Cache und in Hauptspeicher geschrieben: Einfach, garantiert Konsistenz

- 2 Copy-Back (Write-Later)-Strategie: Datum wird nur im Cache aktualisiert und betroffene Cache-Zeile als verändert markiert (Dirty Bit wird auf 1 gesetzt).

- Spätestens vor Ersetzung muss Datum in Hauptspeicher zurückgeschrieben werden (write back, copy back)

- Vorteilhaft z.B. bei viel benutzter Variable (z.B. Schleifencounter)

- System jedoch teilweise inkonsistent

-Caching

### Aktualisierungsstrategien: Schreiben

#### Schreib-Fehltreffer

Auch zwei Möglichkeiten:

- No-Write-Allocate-Strategie: Datum nur in Hauptspeicher schreiben, liegt danach nicht im Cache vor

- Write-Allocate-Strategie: Datum in Hauptspeicher schreiben und zusätzlich den entsprechenden Block in Cache laden

### Überblick

- 1 Einführung und Formale Aspekte Klassifikation Design und Performance Quantitative Methoden

- Standard-Rechnerarchitektur Abstraktionsebenen Prozessor

- Speicherverwaltung Virtueller Speicher und Paging Caching

- 4 Externer Speicher Festplatten Disk Scheduling SSD

- Skalare und superskalare/parallele Architekturen CISC und RISC Pipelining Superskalare Architekturen

### Sekundärspeicher

#### Sekundärspeicher

- Speichermedien mit persistenter (dauerhafter)

Speicherung

- · Optische Medien: CD, DVD, BluRay, ...

# Sekundärspeicher

#### Sekundärspeicher

- Speichermedien mit persistenter (dauerhafter)

Speicherung

- Optische Medien: CD, DVD, BluRay, ...

- Magnetische Medien: Festplatte (HDD), Floppy, ...

# Sekundärspeicher

#### Sekundärspeicher

- Speichermedien mit persistenter (dauerhafter)

Speicherung

- Optische Medien: CD, DVD, BluRay, ...

- Magnetische Medien: Festplatte (HDD), Floppy, ...

- Elektronische Medien: v.a. Flash-Speicher (USB-Stick, SSD, ...)

- · Keine mechanischen Verzögerungen

- Dafür meist unterschiedliche Zeiten für Lesen/Schreiben

- Vor dem Schreiben muss meist gelöscht werden

- Externer Speicher

-Festplatten

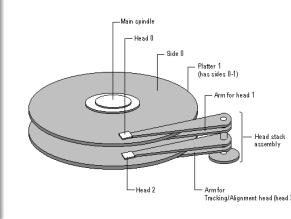

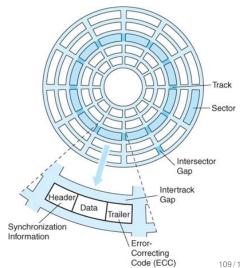

# Festplatten

#### Aufbau

- Mehrere Scheiben (Platter) aus nicht magnetisierbarem Material (Substrate)

- Magnetisierbares Material wird aufgebracht

- Für jeden Platter: Schreib/Leseköpfe auf beweglichem Arm

-Festplatten

### Festplatten

#### Schreiben

- Bewegte Ladungen (=Strom) erzeugen ein Magnetfeld

- Definierter Bereich der Oberfläche wird magnetisiert

- Richtung des Stroms bestimmt Richtung der Magnetisierung (logisch 0/1)

-Festplatten

### Festplatten

#### Schreiben

- Bewegte Ladungen (=Strom) erzeugen ein Magnetfeld

- Definierter Bereich der Oberfläche wird magnetisiert

- Richtung des Stroms bestimmt Richtung der Magnetisierung (logisch 0/1)

#### Lesen

- Veränderliches Magnetfeld induziert Strom in einem Leiter

- Magnetoresistiver (MR) Sensor, Widerstand hängt von Richtung der Magnetisierung ab. Per Lesestrom wird Widerstand (über Spannungsabfall) gemessen

VO 050041: Technische Grundlagen der Informatik

Externer Speicher

Festplatten

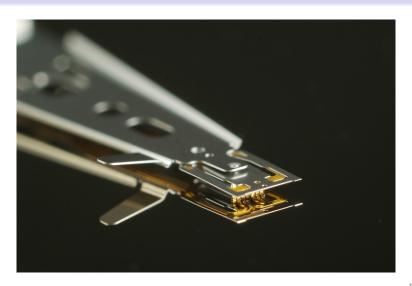

### Disk head

Externer Speicher

Festplatten

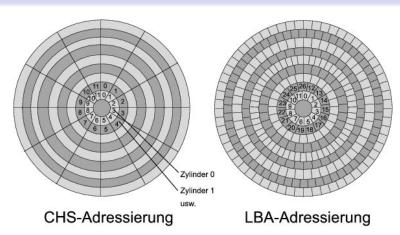

# Aufbau – CHS (Cylinder, Head, Sector) vs. LBA (Logical Block Addressing)

Externer Speicher

Festplatten

# Datenorganisation bei CHS-Adressierung

- Festplatten

# Datenorganisation bei CHS-Adressierung

#### Vereinfacht:

Jeder Platter in viele Spuren (Tracks, konzentrische Kreise) aufgeteilt

# Datenorganisation bei CHS-Adressierung

#### Vereinfacht:

- Jeder Platter in viele Spuren (Tracks, konzentrische Kreise) aufgeteilt

- Jede Spur in viele Sektoren unterteilt. Einheit für Datentransfer

- Sektorgröße früher meist 512 Byte, heute auch oft 4 KiB

Festplatten

### Performance bei CHS-Adressierung

#### Seek Time T<sub>S</sub>

Aktuator (Lese/Schreibkopf) muss auf jeweilige Spur bewegt werden - Festplatten

# Performance bei CHS-Adressierung

#### Seek Time Ts

- Aktuator (Lese/Schreibkopf) muss auf jeweilige Spur bewegt werden

- Abschätzung  $T_S = m \cdot n + s$

- n... Anzahl der überquerten Spuren

- *m*... Zeit pro Spur (Bruchteile einer ms)

- s... Startup-Zeit (wenige ms)

- Meist wird durchschnittliche Seek Time angegeben, ca. 8-15ms

### Performance bei CHS-Adressierung

### Rotationsverzögerung $T_r$

Ist Aktuator auf richtiger Spur, dauert es, bis sich entsprechender Sektor unter dem Aktuator befindet

### Performance bei CHS-Adressierung

### Rotationsverzögerung $T_r$

- Ist Aktuator auf richtiger Spur, dauert es, bis sich entsprechender Sektor unter dem Aktuator befindet

- Abschätzung  $T_r = \frac{1}{2r}$

- r... Umdrehungen pro Minute (RPM)

- Im Durchschnitt ist man eine halbe Rotation von Sektor entfernt

- Bsp r=10000 RPM;  $T_r = \frac{1}{2 \cdot 10000 \, min} = 5 \cdot 10^{-5} \, min = 5 \cdot 10^{-5} \cdot 60 \, s = 3 \cdot 10^{-3} \, s = 3 \, ms$

Externer Speicher

-Festplatten

# Performance bei CHS-Adressierung

#### Transferzeit T

- Reine Übertragungszeit der Daten, Aktuator ist schon an richtiger Position

- Hängt v.a. von RPMs und Datendichte ab

### Performance bei CHS-Adressierung

#### Transferzeit T

- Reine Übertragungszeit der Daten, Aktuator ist schon an richtiger Position

- Hängt v.a. von RPMs und Datendichte ab

- $T = \frac{b}{r \cdot N}$

- b... Anzahl Bytes, die transferiert werden müssen

- N... Anzahl an Bytes auf der Spur

#### Gesamte Transferzeit Ta

$$T_a = T_S + T_r + T = T_S + \frac{1}{2r} + \frac{b}{rN}$$

-Festplatten

# (De-)Fragmentierung

#### Fragmentierung

- Verstreute Speicherung logisch zusammengehörender Datenblöcke des Dateisystems auf einem Datenträger

- Führt speziell bei hohen Zugriffszeiten (seek time, HDD) zu spürbarer Verlangsamung der Lese- und Schreibvorgänge

#### Defragmentierung

- Neuordnung von fragmentierten Datenblöcken

- Logisch zusammengehörende Datenblöcke sollten aufeinander folgen

- Kann den sequentiellen Zugriff beschleunigen

### Disk Scheduling

#### Disk Scheduling

Leistungssteigerung nicht nur durch mechanische Verbesserungen oder Defragmentierung erzielbar

# **Disk Scheduling**

#### Disk Scheduling

- Leistungssteigerung nicht nur durch mechanische Verbesserungen oder Defragmentierung erzielbar

- Scheduling: Gezieltes Umreihen der Anfragen, mechanische Verzögerungen möglichst minimieren

# **Disk Scheduling**

#### Disk Scheduling

- Leistungssteigerung nicht nur durch mechanische Verbesserungen oder Defragmentierung erzielbar

- Scheduling: Gezieltes Umreihen der Anfragen, mechanische Verzögerungen möglichst minimieren

- Strategien: FIFO/FCFS, SSTF, (C-)SCAN, (C)-LOOK

VO 050041: Technische Grundlagen der Informatik

Externer Speicher

Disk Scheduling

# Scheduling: FIFO/FCFS

#### FIFO/FCFS

- First-In-First-Out; First-Come-First-Served

- Anfragen in Reihenfolge des Eintreffens bearbeiten

# Scheduling: FIFO/FCFS

#### FIFO/FCFS

- First–In–First–Out; First–Come–First–Served

- Anfragen in Reihenfolge des Eintreffens bearbeiten

- Vorteil: Faire Abarbeitung

# Scheduling: FIFO/FCFS

#### FIFO/FCFS

- First–In–First–Out; First–Come–First–Served

- Anfragen in Reihenfolge des Eintreffens bearbeiten

- Vorteil: Faire Abarbeitung

- Nachteil: Gesamtanzahl an überquerten Spuren sehr hoch

### Scheduling: SSTF

#### **SSTF**

- Shortest Seek Time First

- Immer Anfrage bearbeiten, deren Spur der momentanen Aktuator-Position am nächsten ist

# Scheduling: SSTF

#### **SSTF**

- Shortest Seek Time First

- Immer Anfrage bearbeiten, deren Spur der momentanen Aktuator-Position am nächsten ist

- Vorteil: Jeweilige Seek Time wird verringert

### Scheduling: SSTF

#### SSTF

- Shortest Seek Time First

- Immer Anfrage bearbeiten, deren Spur der momentanen Aktuator-Position am nächsten ist

- · Vorteil: Jeweilige Seek Time wird verringert

- Nachteil: Durchschnittliche Seek Time nicht garantiert minimal

### Scheduling: (C-)SCAN

#### **SCAN**

- Aktuator läuft immer zwischen Endpositionen auf und ab

- Verhindert, dass Aufträge "verhungern" (Starvation)

#### C-SCAN

- C: Circular

- Wie SCAN, beim Zurückkehren an Anfangsposition wird nichts abgearbeitet

- Reduziert Verzögerung für neu eintreffende Anfragen

# Scheduling: (C-)LOOK

#### LOOK

- Ähnlich zu SCAN, aber intelligenter

- Sobald letzte angefragte Spur einer Richtung erreicht wurde, ändert Aktuator die Laufrichtung

- Restliche, unnötige Spuren müssen also nicht überquert werden

- C-LOOK: Analog

VO 050041: Technische Grundlagen der Informatik

LExterner Speicher

# Beispiel

☐ Disk Scheduling

#### Beispiel

Disk hat insgesamt 200 Spuren

# Beispiel

Disk Scheduling

#### Beispiel

- Disk hat insgesamt 200 Spuren

- In der Warteschlange (Queue) sind mehrere Anfragen

└ Disk Scheduling

### Beispiel

#### Beispiel

- Disk hat insgesamt 200 Spuren

- In der Warteschlange (Queue) sind mehrere Anfragen

- Angefragte Daten belegen jeweils maximal eine Spur

- Aktuator befindet sich gerade auf Spur 100, war davor auf Spur 85 ⇒ aufsteigende Laufrichtung bei LOOK/SCAN

- Folgende Spuren sind zu Lesen:

- 55, 58, 39, 18, 90, 160, 150, 38, 184

### **FIFO**

| Nächste Spur | Differenz |

|--------------|-----------|

| 55           | 45        |

| 58           | 3         |

| 39           | 19        |

| 18           | 21        |

| 90           | 72        |

| 160          | 70        |

| 150          | 10        |

| 38           | 112       |

| 184          | 146       |

| Gesamt       | 498       |

| Schnitt      | 55,3      |

### SSTF

| Nächste Spur | Differenz |

|--------------|-----------|

| 90           | 10        |

| 58           | 32        |

| 55           | 3         |

| 39           | 16        |

| 38           | 1         |

| 18           | 20        |

| 150          | 132       |

| 160          | 10        |

| 184          | 24        |

| Gesamt       | 248       |

| Schnitt      | 27,6      |

### **SCAN**

| Nächste Spur | Differenz |

|--------------|-----------|

| 150          | 50        |

| 160          | 10        |

| 184          | 24        |

| 200          | 16        |

| 90           | 110       |

| 58           | 32        |

| 55           | 3         |

| 39           | 16        |

| 38           | 1         |

| 18           | 20        |

| Gesamt       | 282       |

| Schnitt      | 31,3      |

### C-SCAN

| Nächste Spur | Differenz |

|--------------|-----------|

| 150          | 50        |

| 160          | 10        |

| 184          | 24        |

| 200          | 16        |

| 1            | 199       |

| 18           | 17        |

| 38           | 20        |

| 39           | 1         |

| 55           | 16        |

| 58           | 3         |

| 90           | 32        |

| Gesamt       | 388       |

| Schnitt      | 43,1      |

### LOOK

| Nächste Spur | Differenz |

|--------------|-----------|

| 150          | 50        |

| 160          | 10        |

| 184          | 24        |

| 90           | 94        |

| 58           | 32        |

| 55           | 3         |

| 39           | 16        |

| 38           | 1         |

| 18           | 20        |

| Gesamt       | 250       |

| Schnitt      | 27,8      |

### C-LOOK

| Nächste Spur | Differenz |

|--------------|-----------|

| 150          | 50        |

| 160          | 10        |

| 184          | 24        |

| 18           | 166       |

| 38           | 20        |

| 39           | 1         |

| 55           | 16        |

| 58           | 3         |

| 90           | 32        |

| Gesamt       | 322       |

| Schnitt      | 35,8      |

### Bespiel: Vergleich

|         | FCFS | SSTF | SCAN | C-SCAN | LOOK | C-LOOK |

|---------|------|------|------|--------|------|--------|

| Spuren  | 498  | 248  | 282  | 388    | 250  | 322    |

| Schnitt | 55,3 | 27,6 | 31,3 | 43,1   | 27,8 | 35,8   |

#### Nota bene

Es muss immer durch die Anzahl der zu bearbeitenden Spuren (hier 9) dividiert werden. Wenn ein Verfahren (hier SCAN und C-SCAN) Wege zurücklegt, bei denen keine Arbeit erledigt wird, müssen die in die Summe eingerechnet werden, der Divisor wird aber NICHT erhöht!

### Solid State Drive (SSD)

#### Aufbau

$\sqcup_{\mathsf{SSD}}$

- Durch Halbleiterbausteine realisiertes, nichtflüchtiges Speichermedium (zB. EEPROM, FLASH)

- Üblicherweise teurer als HDDs (per GB)

- Aber auch schneller! (Seek time entfällt)

- Geringer Stromverbrauch, geräuschfrei

- Unempfindlich gegen Erschütterungen, sehr leicht

- Limitierte Anzahl an Schreibvorgängen

- Nur ca. 10<sup>4</sup> 10<sup>6</sup> Schreibvorgänge pro Speicherzelle

- "Wear Leveling"-Algorithmen: Daten werden gleichmäßig auf alle Speicherzellen verteilt

### Überblick

- Einführung und Formale Aspekt Klassifikation Design und Performance Quantitative Methoden

- 2 Standard-Rechnerarchitektur Abstraktionsebenen Prozessor

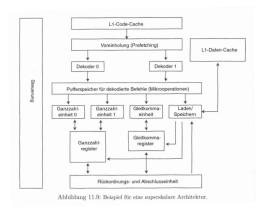

- Speicherverwaltung Virtueller Speicher und Paging Caching